Intel đã tiết lộ kiến trúc mới cho hai lõi CPU x86, hai hệ thống trên vi mạch (SoC) của trung tâm dữ liệu, hai bộ vi xử lý GPU rời và một kiến trúc hiệu suất lai đa lõi mang tính cách mạng đối với khách hàng.

Kiến trúc tựa như thuật giả kim của phần cứng và phần mềm vậy. Lĩnh vực này tập hợp các bóng bán dẫn tốt nhất của một động cơ nhất định, kết nối chúng thông qua công nghệ đóng gói tiên tiến, tích hợp bộ nhớ đệm băng thông cao và bộ nhớ đệm năng lượng thấp, kèm theo trang bị bộ nhớ dung lượng lớn với độ trễ thấp cho kiến trúc cụm máy tính (clusters) trong một thể thống nhất, đồng thời đảm bảo toàn bộ phần mềm được cải thiện tốc độ một cách trơn tru. Công bố những đổi mới kiến trúc cho các sản phẩm sắp ra mắt là điều mà các kiến trúc sư của Intel luôn mong đợi tại sự kiện Architecture Day hàng năm. Năm nay – tại lần thứ ba diễn ra sự kiện – là lần mang lại nhiều điều thú vị nhất.

Hôm nay, chúng tôi đã tiết lộ những thay đổi lớn nhất của kiến trúc Intel trong vòng một thế hệ qua. Điều này bao gồm chia sẻ chuyên sâu đầu tiên về Alder Lake, kiến trúc kết hợp hiệu suất đầu tiên của chúng tôi với hai thế hệ lõi x86 mới và bộ lập lịch khối lượng công việc Intel® Thread Director thông minh; Sapphire Rapids, kiến trúc trung tâm dữ liệu với thiết lập tiêu chuẩn mới của Intel bao gồm các lõi hiệu suất mới và các công cụ tăng tốc khác nhau ; kiến trúc GPU riêng biệt xử lý đồ họa và chơi game (GPU) mới; các đơn vị xử lý cơ sở hạ tầng mới (IPU) và Pointe Vecchio, kiến trúc GPU trung tâm dữ liệu tour-de-force với mật độ tính toán cao nhất từ trước đến nay của Intel.

Những đột phá về hệ thống kiến trúc lần này đã tạo tiền đề cho một kỷ nguyên đi đầu về sản phẩm của Intel, và điều đó sẽ sớm bắt đầu với Alder Lake. Những cải tiến mà chúng tôi đã tiết lộ tại Architecture Day cho thấy kiến trúc sẽ đáp ứng nhu cầu ngày càng cao về hiệu suất điện toán khi khối lượng công việc từ máy tính để bàn đến trung tâm dữ liệu trở nên lớn hơn, phức tạp hơn và đa dạng hơn bao giờ hết.

Các kiến trúc sư của chúng tôi đang làm việc rất chăm chỉ. Họ kết hợp các công cụ đa dạng và độc đáo của Intel trong tính toán vô hướng, vectơ, ma trận và không gian (spatial compute engines) để tạo ra các kiến trúc điện toán lai mang lại lợi ích phi tuyến tính trên những yêu cầu khắt khe nhất của khách hàng.

Những thông tin nổi bật của sự kiện:

Efficient x86 Core: Vi kiến trúc x86 với khả năng nâng cao hiệu suất có thể xử lý mọi nhu cầu điện toán, nhằm đáp ứng triệt để mọi yêu cầu của khách hàng, từ các ứng dụng di động công suất thấp đến các vi dịch vụ đa lõi. So với Skylake, vi xử lý tiên tiến nhất của Intel, Efficient core mang lại hiệu suất cao hơn 40% ở cùng công suất điện hoặc có hiệu suất ngang bằng trong khi tiêu thụ ít hơn 40% điện năng. 1 Đối với hiệu suất băng thông, bốn lõi Efficient cores mang lại hiệu suất cao hơn 80% trong khi vẫn tiêu thụ ít năng lượng hơn hai lõi Skylake chạy bốn luồng, hoặc đạt được cùng hiệu suất băng thông trong khi tiêu thụ ít hơn 80% điện năng.

Performance x86 Core: Lõi x86 này không chỉ là lõi CPU có hiệu suất cao nhất mà Intel từng chế tạo, mà nó còn là một bước tiến về hiệu năng trong kiến trúc CPU nhằm thúc đẩy quá trình xử lý điện toán trong thập kỷ tới. Performance x86 Core được thiết kế với một kiến trúc rộng, sâu và thông minh hơn để thích hợp tính toán song song cũng như tăng khả năng thao tác các dữ liệu song song, giảm độ trễ và tăng hiệu năng toàn diện. Lõi X86 cũng hỗ trợ một lượng lớn dữ liệu và các ứng dụng mã footprint. Geomean tại Performance Core được cải thiện khoảng 19%trên một loạt các tác vụ so với kiến trúc Core thế hệ thứ 11 hiện tại của chúng tôi (lõi Cypress Cove) ở cùng một tần suất.

Với mục đích hướng tới các bộ xử lý trung tâm dữ liệu và các xu hướng mới sẽ hình thành trong machine learning, Performance-core mang đến phần cứng chuyên dụng, bao gồm tính năng mở rộng ma trận nâng cao (Advanced Matrix Extensions – AMX) mới của Intel, để thực hiện các tác vụ nhân ma trận tại thứ tự hiệu suất lớn – tăng gần gấp 8 lần trí tuệ nhân tạo tăng tốc. Khả năng này được thiết lập để phần mềm dễ sử dụng, tận dụng mô hình lập trình x86.

Hệ thống Phân Luồng của Intel (Intel Thread Director): Phương pháp lập lịch độc đáo của Intel được phát triển để đảm bảo Nhân hiệu năng (Efficient core) và Nhân tiết kiệm (Performance core) hoạt động liền mạch với nhau, phân bổ khối lượng công việc một cách linh hoạt và thông minh ngay từ đầu, tối ưu hóa hệ thống để đạt hiệu năng và công suất tối đa trong thực tế. Với khả năng trí tuệ được tích hợp trực tiếp vào lõi – đảm bảo hoạt động trơn tru với hệ điều hành để phân chia đúng luồng vào đúng lõi vào đúng thời điểm thích hợp.

Alder Lake: Nhằm tái định nghĩa kiến trúc đa lõi, Alder Lake sẽ là kiến trúc hiệu năng lai đầu tiên của Intel với Công nghệ Intel Thread Director mới. Đây là kiến trúc dành cho khách hàng với hệ thống trên vi mạch (SoC) thông minh nhất của Intel có sự kết hợp giữa Nhân hiệu năng cao và Nhân tiết kiệm điện, mở rộng quy mô từ siêu di động sang máy tính để bàn và dẫn đầu quá trình chuyển đổi trong ngành với I / O và bộ nhớhang đầu trong ngành. Bộ vi xử lý Alder Lake sẽ “xuất xưởng” trong năm nay.

Xe HPG và Alchemist SoC: Một vi kiến trúc đồ họa riêng biệt mới được thiết kế để nâng tầm hiệu suất “đỉnh cao”, phù hợp cho những game thủ và những người làm sáng tạo. Vi kiến trúc Xe HPG có Xe-core mới, một phần tử tập trung vào điện toán, có thể lập trình và mở rộng, đồng thời hỗ trợ đầy đủ cho DirectX 12 Ultimate. Động cơ ma trận mới bên trong các lõi Xe (gọi tắt là XMX – Xe Matrix eXtensions) tăng tốc các tác vụ Trí tuệ nhân tạo như XeSS và là một công nghệ nâng cấp mới cho phép chơi game có hiệu suất và độ trung thực cao. Các SoC Alchemist dựa trên Xe HPG (tên mã trước đây là DG2) sẽ được tung ra thị trường vào Quý 1 năm 2022 dưới cái tên của một thương hiệu mới, Intel Arc brand.

Sapphire Rapids: Kết hợp các lõi hiệu năng của Intel với các lõi tăng tốc mới, Sapphire Rapids đã thiết lập lại tiêu chuẩn cho các bộ xử lý trung tâm dữ liệu thế hệ mới. Sapphire Rapids nổi bật với kiến trúc mạng lưới mô-đun SoC, sở hữu khả năng cải thiện hiệu suất đáng kể trong khi vẫn duy trì tiện ích của giao diện CPU nguyên khối nhờ công nghệ đóng gói kết nối đa khuôn EMIB của Intel và kiến trúc lưới tiên tiến.

Bộ xử lý cơ sở hạ tầng (IPU): Mount Evens là IPU dựa trên ASIC chuyên dụng đầu tiên của Intel, cùng với nền tảng tham chiếu IPU dựa trên FPGA mới, có tên Oak Springs Canyon. Với kiến trúc dựa trên IPU của Intel, các nhà cung cấp dịch vụ đám mây (CSP) có thể tối đa hóa doanh thu từ trung tâm dữ liệu bằng cách giảm tải các tác vụ cơ sở hạ tầng từ CPU sang IPU. Việc tải các nhiệm vụ cơ sở hạ tầng cho IPU cho phép các CSP cho khách hàng thuê 100% CPU máy chủ của họ.

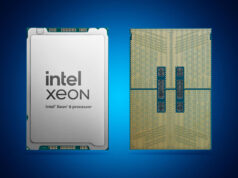

Xe HPC, Ponte Vecchio: Đây là SoC phức tạp nhất mà Intel từng chế tạo và là một ví dụ tuyệt vời về cách chúng tôi ứng dụng chiến lược IDM 2.0 trong thực tiễn. Ponte Vecchio tận dụng các quy trình bán dẫn tiên tiến nhất, công nghệ kết nối đa khuôn EMIB mang tính cách mạng và quy trình đóng gói 3D Foveros. Với sản phẩm này, chúng tôi dự định sẽ hiện thực hóa dự án moon-shot, một thiết bị bao gồm một trăm tỷ bóng bán dẫn cung cấp FLOP và mật độ điện toán hàng đầu trong ngành để đẩy mạnh phát triển Trí tuệ nhân tạo, Điện toán hiệu suất cao (HPC) cũng như hỗ trợ các tác vụ cần phân tích nâng cao. Tại sự kiện Architecture Day, chúng tôi đã chứng minh hiệu suất dẫn đầu của silicon Ponte Vecchio, lập kỷ lục trong ngành về cả băng thông suy luận và đào tạo (inference & training) trên mốc tiêu chuẩn phổ biến của Trí tuệ nhân tạo. 1 Silicon A0 có thể cung cấp băng thông mạnh hơn 45 TFLOPS FP32, lớn hơn băng thông Bộ nhớ 5 TBps và sở hữu khả năng kết nối lớn hơn 2 TBps. Ponte Vecchio, cũng như với các kiến trúc Xe của chúng tôi, sẽ được kích hoạt bởi lập trình đa kiến trúc mở đạt tiêu chuẩn oneAPI, đồng thời là nơi xếp chồng phần mềm hợp nhất giữa các nhà cung cấp.

Nhìn lại một năm qua, có thể thấy công nghệ đã trở thành một nhân tố quan trọng trong cách chúng ta giao tiếp, làm việc, giải trí và ứng phó với đại dịch. Quy mô điện toán tầm cỡ đã được chứng minh là rất cần thiết. Sắp tới, chúng ta sẽ tiếp tục phải đối mặt với nhu cầu lớn về điện toán – có khả năng gấp 1.000 lần vào năm 2025. Mức tăng 1.000 lần trong 4 năm chính là Định luật Moore theo lũy thừa bậc 5.

Giám đốc điều hành của Intel và cũng là một kiến trúc sư, Pat Gelsinger, phát biểu tại Architecture Day rằng “Chúng ta đang phải đối mặt với những thách thức khó khăn về điện toán mà chỉ kiến trúc và những nền tảng mang tính cách mạng có thể giải quyết được… Với nỗ lực của những kiến trúc sư và kỹ sư tài năng của chúng tôi, tất cả những điều kỳ diệu về công nghệ này đã thành hiện thực.”

Thế giới đang trông cậy vào các kiến trúc sư và kỹ sư để giải quyết các vấn đề điện toán khó nhằn, từ đó cải thiện chất lượng cuộc sống. Chúng tôi sẽ tiếp tục đẩy mạnh quá trình hình thành chiến lược và thực thi kế hoạch để đáp ứng những nhu cầu này – bất chấp mọi khó khăn đi kèm trong hành trình đó.

Raja M. Koduri Phó chủ tịch cấp cao kiêm Tổng giám đốc Mảng Tăng tốc Hệ thống Điện toán và Đồ họa (AXG) tại Tập đoàn Intel.